TI PGA450-Q1超声波汽车倒车解决方案涵电路图介绍

TI 企业的PGA450-Q1是全集成化超音波感应器插口元器件,集成化了电压稳压器,12位SAR ADC,8位微处理器,数据带通过滤器,DAC,2个NMOS低边控制器,低噪声放大仪,震荡器,LIN 2.1物理学通讯协议插口.关键适用于车辆停车, 盲区检测和物品检验.文中详细介绍了PGA450-Q1关键特点,作用程序框图, 运用原理图, 评定板PGA450-Q1 EVM关键特点,原理图和PCB布局.

The PGA450-Q1 is a fully integrated interface device for ultrasonic transducers used in automoTIve park distance or object detecTIon applicaTIons. It incorporates these system blocks: voltage regulators, a 12-bit SAR ADC, an 8-bit microcontroller, a digital band-pass filter, a DAC, dual NMOS low-side drivers, a low-noise amplifier, an oscillator, and a LIN 2.1 physical interface and protocol for interfacing.

The PGA450-Q1 possesses an 8-bit microcontroller and OTP memory for program storage for processing the echo signal and calculaTIng the distance between the transducer and the object. This data is transmitted through the LIN 2.1 communication protocol. The LIN 2.1 physical layer is slave-only and does not implement the LIN wake-up feature.

PGA450-Q1关键特点:

Dual NMOS Low-Side Drivers

Configurable Burst Generator

Low-Noise Amplifier

12-Bit SAR ADC

Configurable Digital Band-Pass Filter

Digital Signal Envelope Detect

On-Chip 8-Bit Microprocessor

LIN 2.1 Physical Interface and Protocol

Watchdog Timer

Four-Wire SPI for Testability / Programming

8K Bytes OTP

768 Bytes of FIFO RAM

256 Bytes Scratchpad RAM

8K Bytes of Development RAM

32 Bytes of EEPROM for Application

PGA450-Q1运用:

Automotive Park Distance

Blind Spot Detection

Object Detection Applications

图1.PGA450-Q1作用程序框图

The digital data path has the following components:

? Band-pass filter

? Rectifier

? Peak extractor

? Downsampler

? Low-pass filter

图2.PGA450-Q1数据数据通路程序框图

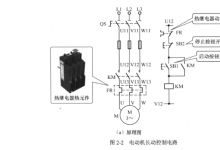

图3.PGA450-Q1运用原理图

评定板PGA450-Q1 EVM

This user’s guide describes the characteristics, operation, and use of the PGA450-Q1 EVM.

评定板PGA450-Q1 EVM关键特点:

? Single power-supply input for basic operation

? Example single-ended transformer and 58-kHz transducer

? LIN master transceiver

? RS-232 transceiver for UART testing and debug

? PC control with a graphical user interface and USB communications board

?

图4.评定板PGA450-Q1 EVM外观设计图

图5.评定板PGA450-Q1 EVM原理图:LIN

图6.评定板PGA450-Q1 EVM原理图:开关电源

图7.评定板PGA450-Q1 EVM原理图:RS232

图8.评定板PGA450-Q1 EVM原理图:USB控制板

图9.评定板PGA450-Q1 EVM原理图: PGA450-Q1

图10.评定板PGA450-Q1 EVM PCB布局:高层

图11.评定板PGA450-Q1 EVM PCB布局:最底层

上一篇:双路时控开关实物接线图(多图)

最新更新

猜你喜欢

电工推荐

PLC学习资料

PLC学习资料  电工基础知识

电工基础知识  电工技术基础

电工技术基础 电工维修知识

电工维修知识  电工安全知识

电工安全知识  电工考证知识

电工考证知识  电工学习网

电工学习网 电工技术基础

电工技术基础