解读多间隔脉冲信号连接器电路

单片机设计系统软件工作中时,除开进到操作系统一切正常的重置以外,当因为程序执行错误或操作方法不正确使体系处在死锁情况时,为改变现状,也需按复位开关以重启。因此系统软件的延时电路务必精确、靠谱地工作中。单片机设计的回位基本都是靠外界线路完成的,在晶振电路运行后,只需在51单片机的RST脚位上发生24个数字时钟振动单脉冲(即两个振荡周期)之上的上拉电阻,单片机设计便完成复位情况校准。为了更好地确保软件系统安全可靠地校准,系统软件使用功能键脉冲信号校准方法。

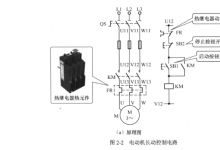

单片机设计AT89S52的P1口与液晶显示屏控制模块LCD1602的数据信息端口号相接,P3.2操纵液晶显示模块的读写能力;饱和度调节端联接一个10 kΩ的可变电阻,用于调节液晶显示屏色度。此外,单片机设计的P2口与CPLD的八个I/O口相接,以开展传输数据,其电路原理如图2所显示。

CPLD电路原理

晶振电路是为CPU给予頻率标准的电子器件,归属于系统软件必不可少的一部分。一般分成有源晶振和微波感应器晶振电路2个大类,微波感应器晶振电路规定集成ic里面有振荡器,而且其数据信号工作电压依据起振电源电路而定,容许不一样的工作电压,但微波感应器晶振电路一般数据信号品质和精密度较弱,必须精准的配对外围电路,如需拆换晶振电路要一起拆换外围电路。有源晶振不用集成ic的內部震荡器,能够给予高精密的頻率标准,数据信号品质也较无源晶振电路好些。

EPM7128SLC84必须给予外界时钟信号,因为CPLD对数字时钟精密度规定甚高,根据之前的剖析得知有源晶振的通讯品质和精密度较无源晶振电路高,因此选用1.000 MHz的数字功放晶振电路,电源电路的输入输出端口号与CPUEPM7128SLC84的GCKL1联接,其实际电路原理如图所示3所显示。

最新更新

猜你喜欢

电工推荐

PLC学习资料

PLC学习资料  电工基础知识

电工基础知识  电工技术基础

电工技术基础 电工维修知识

电工维修知识  电工安全知识

电工安全知识  电工考证知识

电工考证知识  电工学习网

电工学习网 电工技术基础

电工技术基础