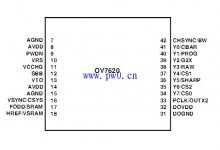

stc89c52引脚图及引脚功用

VCC(40引脚):电源电压

VSS(20引脚):接地

P0端口(P0.0~P0.7,39~32引脚):P0口是一个漏极开路的8位双向I/O口。作为输出端口,每个引脚能驱动8个TTL负载,对端口P0写入“1”时,能够作为高阻抗输入。在拜访外部程序和数据存储器时,P0口也能够供给低8位地址和8位数据的复用总线。此刻,P0口内部上拉电阻有用。在Flash ROM编程时,P0端口接纳指令字节;而在校验程序时,则输出指令字节。验证时,恳求外接上拉电阻。

P1端口(P1.0~P1.7,1~8引脚):P1口是一个带内部上拉电阻的8位双向I/O口。P1的输出缓冲器可驱动(吸收或许输出电流办法)4个TTL输入。对端口写入1时,经过内部的上拉电阻把端口拉到高电位,这是可用作输进口。P1口作输进口运用时,因为有内部上拉电阻,那些被外部拉低的引脚会输出一个电流。

此外,P1.0和P1.1还能够作为守时器/计数器2的外部技能输入(P1.0/T2)和守时器/计数器2的触发输入(P1.1/T2EX),详细拜见下表:

在对Flash ROM编程和程序校验时,P1接纳低8位地址。

表XX P1.0和P1.1引脚复用功用

| 引脚号 | 功用特性 |

| P1.0 | T2(守时器/计数器2外部计数输入),时钟输出 |

| P1.1 | T2EX(守时器/计数器2捕获/重装触发和方向操控) |

P2端口(P2.0~P2.7,21~28引脚):P2口是一个带内部上拉电阻的8位双向I/O端口。P2的输出缓冲器能够驱动(吸收或输出电流办法)4个TTL输入。对端口写入1时,经过内部的上拉电阻把端口拉到高电平,这时可用作输进口。P2作为输进口运用时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。

在拜访外部程序存储器和16位地址的外部数据存储器(如实施“MOVX @DPTR”指令)时,P2送出高8位地址。在拜访8位地址的外部数据存储器(如实施“MOVX @R1”指令)时,P2口引脚上的内容(即是专用寄存器(SFR)区中的P2寄存器的内容),在悉数拜访时期不会改动。

在对Flash ROM编程和程序校验时期,P2也接纳高位地址和一些操控信号。

P3端口(P3.0~P3.7,10~17引脚):P3是一个带内部上拉电阻的8位双向I/O端口。P3的输出缓冲器可驱动(吸收或输出电流办法)4个TTL输入。对端口写入1时,经过内部的上拉电阻把端口拉到高电位,这时可用作输进口。P3做输进口运用时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输入一个电流。

在对Flash ROM编程或程序校验时,P3还接纳一些操控信号。

P3口除作为通常I/O口外,还有别的一些复用功用,如下表所示:

表XX P3口引脚复用功用

| 引脚号 | 复用功用 |

| P3.0 | RXD(串行输进口) |

| P3.1 | TXD(串行输出口) |

| P3.2 | (外部接连0) |

| P3.3 | (外部接连1) |

| P3.4 | T0(守时器0的外部输入) |

| P3.5 | T1(守时器1的外部输入) |

| P3.6 | (外部数据存储器写选通) |

| P3.7 | (外部数据存储器读选通) |

stc89c52具有以下规范功用: 8k字节flash,256字节ram, 32 位i/o 口线,看门狗守时器,2 个数据指针,三个16 位 守时器/计数器,一个6向量2级接连构造,全双工串行口,片内晶振及时钟电路。别的,stc89c52可降至0hz静态逻辑操作,支撑2种软件可挑选节省用电办法。闲暇办法下,cpu 接轮作业,容许ram、守时器/计数器、串口、接连继续作业。掉电维护办法下,ram内容被保留,振动器被冻住,单片机悉数作业接连,直到下一个接连或硬件复位接连。8 位微操控器 8k字节在体系可编程 flash p0 口:p0口是一个8位漏极开路的双向i/o口。作为输出口,每位能驱动8个ttl逻辑电平。对p0端口写“1”时,引脚用作高阻抗输入。 当拜访外部程序和数据存储器时,p0口也被作为低8位地址/数据复用。在这种办法下, p0具有内部上拉电阻。 在flash编程时,p0口也用来接纳指令字节;在程序校验时,输出指令字节。程序校验时,需求外部上拉电阻。 p1 口:p1 口是一个具有内部上拉电阻的8 位双向i/o 口,p1 输出缓冲器能驱动4 个 ttl 逻辑电平。对p1 端口写“1”时,内部上拉电阻把端口拉高,此刻能够作为输进口运用。作为输入运用时,被外部拉低的引脚因为内部电阻的要素,将输出电流(iil)。此外,p1.0和p1.2别离作守时器/计数器2的外部计数输入(p1.0/t2)和时器/计数器2 的触发输入(p1.1/t2ex),详细如下表所示。 在flash编程和校验时,p1口接纳低8位地址字节。引脚号第二功用 p1.0 t2(守时器/计数器t2的外部计数输入),时钟输出 p1.1 t2ex(守时器/计数器t2的捕捉/重载触发信号和方向操控) p1.5 mosi(在线体系编程用) p1.6 miso(在线体系编程用) p1.7 sck(在线体系编程用) p2 口:p2 口是一个具有内部上拉电阻的8 位双向i/o 口,p2 输出缓冲器能驱动4 个 ttl 逻辑电平。对p2 端口写“1”时,内部上拉电阻把端口拉高,此刻能够作为输进口运用。作为输入运用时,被外部拉低的引脚因为内部电阻的要素,将输出电流(iil)。 在拜访外部程序存储器或用16位地址读取外部数据存储器(例如实施movx @dptr) 时,p2 口送出高八位地址。在这种运用中,p2 口运用很强的内部上拉发送1。在运用 8位地址(如movx @ri)拜访外部数据存储器时,p2口输出p2锁存器的内容。在flash编程和校验时,p2口也接纳高8位地址字节和一些操控信号。 p3 口:p3 口是一个具有内部上拉电阻的8 位双向i/o 口,p2 输出缓冲器能驱动4 个 ttl 逻辑电平。对p3 端口写“1”时,内部上拉电阻把端口拉高,此刻能够作为输进口运用。作为输入运用时,被外部拉低的引脚因为内部电阻的要素,将输出电流(iil)。 p3口亦作为stc89c52分外功用(第二功用)运用,如下表所示。在flash编程和校验时,p3口也接纳一些操控信号。 端口引脚 第二功用 p3.0 rxd(串行输进口) p3.1 txd(串行输出口) p3.2 into(外接连0) p3.3 int1(外接连1) p3.4 to(守时/计数器0) p3.5 t1(守时/计数器1) p3.6 wr(外部数据存储器写选通) p3.7 rd(外部数据存储器读选通) 此外,p3口还接纳一些用于flash闪存编程和程序校验的操控信号。 rst——复位输入。当振动器作业时,rst引脚呈现两个机器周期以上高电平将是单片机复位。 ale/prog——当拜访外部程序存储器或数据存储器时,ale(地址锁存容许)输出脉冲用于锁存地址的低8位字节。通常状况下,ale仍以时钟振动频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于守时意图。要留神的是:每逢拜访外部数据存储器时将越过一个ale脉冲。 对flash存储器编程时期,该引脚还用于输入编程脉冲(prog)。 如有必要,可经过对分外功用寄存器(sfr)区中的8eh单元的d0方位位,可阻遏ale操作。该方位位后,只需一条movx和movc指令才干将ale激活。此外,该引脚会被弱小拉高,单片机实施外部程序时,应设置ale阻遏位无效。 psen——程序贮存容许(psen)输出是外部程序存储器的读选通讯号,当stc89c52由外部程序存储器取指令(或数据)时,每个机器周期两次psen有用,即输出两个脉冲,在此刻期,当拜访外部数据存储器,将越过两次psen信号。 ea/vpp——外部拜访容许,欲使cpu仅拜访外部程序存储器(地址为0000h-ffffh),ea端有必要坚持低电平(接地)。需留神的是:假定加密位lb1被编程,复位时内部会锁存ea端状况。 如ea端为高电平(接vcc端),cpu则实施内部程序存储器的指令。 flash存储器编程时,该引脚加上+12v的编程容许电源vpp,当然这有必要是该器材是运用12v编程电压vpp。

上一篇:双面线路板制作电路图及孔化机理

下一篇:y1电容和y2电容的差异

最新更新

推荐阅读

猜你喜欢

电工推荐

PLC学习资料

PLC学习资料  电工基础知识

电工基础知识  电工技术基础

电工技术基础 电工维修知识

电工维修知识  电工安全知识

电工安全知识  电工考证知识

电工考证知识  电工学习网

电工学习网 电工技术基础

电工技术基础